HIL-NETX50

NETX 50

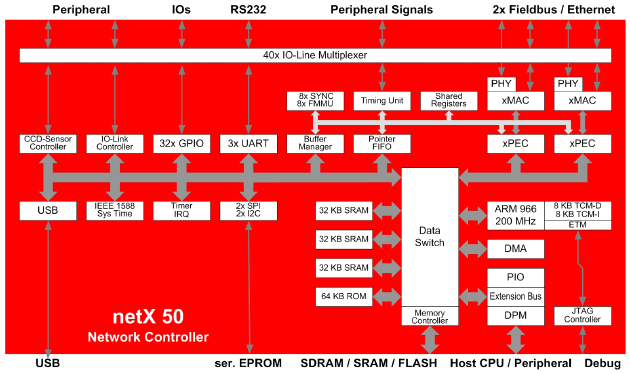

| netX 50 Netzwerk Controller Der netX ist ein hoch integrierter Netzwerk Controller mit einer neuen, auf Kommunikation und maximalen Datendurchsatz optimierten Systemarchitektur. Über ein integriertes Dual-Port-Memory arbeitet er als Companion Chip an einer Host-CPU und realisert das gesamte Spektrum an industrieller Kommunikation vom Feldbussystem bis zu den unterschiedlichen Real-Time-Ethernet Systemen. Rechtfertigt die Applikation keine eigene CPU kann das Host-Interface als Extension Bus zum Anschluß von Peripheriebausteinen oder direkt als digitale Ein- und Ausgänge konfiguriert werden. Die mit 200 MHz getaktete 32-Bit CPU ARM 966E-S verfügt über 112 KB internen RAM und 64 KByte ROM Speicher. Dieser kann über den 32-Bit Memory-Controller extern mit SDRAM, SRAM oder FLASH flexibel erweitert werden. Umfangreiche Peripheriefunktionen, serielle Schnittstellen wie UART, USB, SPI, I²C, sowie der integrierte IO-Link- und CCD-Controller erlauben ein großes Spektrum an Einsatzmöglichkeiten. Der zentrale Daten Switch und die frei konfigurierbaren Kommunikationskanäle mit ihrer eigenen Intelligenz sind das Alleinstellungsmerkmal des netX als ‘high end’ Netzwerk Controller. Der Daten Switch verbindet über fünf Datenpfade die ARM CPU und die Kommunikations-, Host- und DMA-Controller mit dem Speicher oder den Peripherieeinheiten. Dadurch übertragen die Controller ihre Daten parallel, im Gegensatz zu traditionellen, sequentiellen Architekturen mit nur einem gemeinsamen Datenbus und zusätzlichen Buszuteilungszyklen. Die Controller der beiden Kommunikationskanäle sind zweistufig aufgebaut und untereinander identisch. Sie bestehen aus dedizierten ALUs und speziellen Logikeinheiten, die über Microcode ihre jeweilige Protokollfunktion zugewiesen bekommen. Für Ethernet sind die PHYs integriert, so dass die externe Beschaltung sich für Ethernet auf passive Komponnenten wie Übertrager und RC-Glieder reduziert. Der Medium-Access-Controller xMAC sendet bzw. empfängt Daten gemäß dem jeweiligen Buszugriffsverfahren und kodiert bzw. konvertiert diese in eine Byte-Darstellung. Der Protocol-Execution-Controller xPEC fasst diese zu Datenpaketen zusammen und steuert den Telegrammverkehr. Große Datenmengen werden per DMA blockweise in bzw. aus dem Speicher der ARM transportiert, während für Statusinformation jedem Kanal ein Dual-Port-Memory zur Verfügung steht. Alternativ ist eine Tripple-Buffer Logik implementiert, die für einen konfliktfreien Datenaustausch immer die Adresse des nächsten freien Puffers liefert. Mit den intelligenten Kommunikations-ALUs realisiert der netX die unterschiedlichsten Protokolle und Protokoll-Kombinationen in einem Chip - ein absolutes Novum in der industriellen Kommunikationstechnik. |

Fakten auf einen Blick

|

|

| Produkt | NETX 50 | |

|---|---|---|

| Beschreibung | netX 50 Netzwerk Controller | |

| Rechnerkern | ||

| Prozessor | ARM 966E-S, 200 MIPS, ARMv5TE-Befehlssatz mit DSP-Erweiterung | |

| Tightly Coupled Memory | 8 KByte Daten 8 KByte Instruction |

|

| Interner Speicher | ||

| RAM | 96 KByte | |

| ROM | 64 KByte mit Bootloader | |

| Ethernet-Interface | ||

| Ports | 2 x 10BASE-T/100BASE-TX, Half-/Full-Duplex, IEEE 1588 Zeitstempel | |

| PHY | Integriert, Auto-Negotiation, Auto-Crossover | |

| Real-Time-Ethernet | EtherCAT mit acht FMMUs und acht Sync-Manager Ethernet/IP Modbus TCP Powerlink mit integriertem Hub PROFINET RT und IRT mit integriertem Switch SERCOS-III |

|

| Feldbus-Interface | ||

| System | Die Systeme können beliebig kombiniert werden. AS-interface, nur Master CANopen, Master und Slave CC-Link, nur Slave DeviceNet, Master und Slave PROFIBUS, Master und Slave |

|

| Peripherie | ||

| IO-Link Controller | 8 Kanäle, automatische Richtungssteuerung | |

| CCD-Sensor Controller | max. 50 MHz, 640x480 Bildpunkte, frei konfigurierbare Datenformate | |

| IEEE 1588 Systemzeit | 32 Bit Sekundenzähler, 32 Bit Nanosekundenzähler | |

| USB | Revision 1.1, 12 MBaud Full-Speed, Host- oder Device-Mode | |

| UART | 16550 kompatibel, max. 3 MBaud, RTS/CTS Unterstützung, Anzahl: 3 | |

| I²C | Master- und Slave Mode, 50 KHz bis 3.4 MHz, 16 Bit FIFO, Anzahl 2 | |

| SPI | Master- und Slave-Mode, max. 10 MHz, 3 Chip-Select-Signale | |

| Allgemeine E/As | 3.3 V / 6 mA Anzahl 32 |

|

| Status LEDs | 2 LEDs zweifarbig, 3.3 V/9 mA, Anzahl 2 | |

| Speicher-Interface | ||

| Speicherbus | 32 Bit-Datenbus/24 Bit-Adressbus | |

| Adressbereich | 256 MByte SDRAM/64 MByte FLASH | |

| Speicherbausteine | SDRAM, SRAM, FLASH | |

| Host-Interface | ||

| Dual-Port-Memory Mode | 8 / 16 / 32-Bit-Datenbus, konfigurierbar, emuliert durch internes RAM | |

| Extension-Mode | 8/16 Bit-Datenbus, 24 Bit-Adressbus, Bustiming einstellbar | |

| PIO-Mode | Frei programmierbare Ein- und Ausgänge, Anzahl: 53 | |

| Debug-Interface | ||

| JTAG | ARM-Prozessor und Boundary-Scan | |

| ETM | Embedded Trace Macrocell, ETM9 V2 Medium Size | |

| Betriebsbedingungen/Gehäuse/diverse Daten | ||

| Systemtakt | 200 MHz ARM / 100 MHz Peripherie | |

| Signalpegel | 3.3 V | |

| Spannungsversorgung | 1.5 V für Core 3.3 V für Ein-/Ausgänge |

|

| Betriebstemperatur | ohne Kühlkörper –40°C..+70°C mit Kühlkörper 10°/W –40°C..+85°C |

|

| Lagerungstemperatur | -65°C..+150°C | |

| Leistungsaufnahme | PHYs abgeschaltet 0.8 W PHYs eingeschaltet 1.2 W |

|

| Gehäuse | PBGA, 1 mm Raster 324 Pins Maße 19 x 19 mm |

|

Copyright 2014 - Hilscher

Rev: 01/19

Sie haben Ihr Passwort vergessen?

Sie haben Ihr Passwort vergessen?