HIL-NETX100

NETX 100

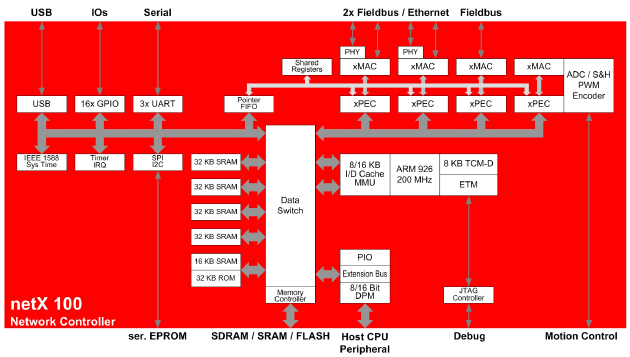

| netX 100 Netzwerk Controller Der Der netX ist ein hoch integrierter Netzwerk Controller mit einer neuen, auf Kommunikation und maximalen Datendurchsatz optimierten Systemarchitektur. Basierend auf die mit 200 MHz getaktete 32-Bit CPU ARM 926EJ-S verfügt er über Memory Management Unit, Caches, DSP- und Java Erweiterungen. Der interne Speicher von 144 KByte RAM und 32 KByte ROM, der den Bootloader enthält ist für kleinere Applikationen ausreichend, während für Windows CE und Linux über den 32-Bit Memory-Controller Speicher extern mit SDRAM, SRAM oder FLASH erweitert wird. Die Anbindung an einen übergeordneten Host erfolgt über das Dual-Port-Memory Interface, welches für stand-alone Applikationen auch als 16-Bit Erweiterungsbus konfigurierbar ist. Umfangreiche Peripheriefunktionen, serielle Schnittstellen wie UART, USB, SPI, I²C, sowie AD-Wandler, PWM und Encoder-Eingänge erlauben ein großes Spektrum an Einsatzmöglichkeiten. Jedoch erst der zentrale Daten Switch und die vier frei konfigurierbaren Kommunikationskanäle mit ihrer eigenen Intelligenz sind das Alleinstellungsmerkmal des netX als ‘high end’ Netzwerk Controller. Der Daten Switch verbindet über vier Datenpfade die ARM CPU und die Kommunikations und Host-Controller mit dem Speicher oder den Peripherieeinheiten. Dadurch übertragen die Controller ihre Daten parallel, im Gegensatz zu traditionellen, sequentiellen Architekturen mit nur einem gemeinsamen Datenbus und zusätzlichen Buszuteilungszyklen. Die Controller der vier Kommunikationskanäle sind zweistufig aufgebaut und untereinander identisch. Sie bestehen aus dedizierten ALUs und speziellen Logikeinheiten, die über Microcode ihre jeweilige Protokollfunktion zugewiesen bekommen. Für Ethernet enthalten zwei Kanäle zusätzlich einen integrierten PHY. Der Medium-Access-Controller xMAC sendet bzw. empfängt Daten gemäß dem jeweiligen Buszugriffsverfahren und kodiert bzw. konvertiert diese in eine Byte-Darstellung. Der Protocol-Execution-Controller xPEC fasst diese zu Datenpaketen zusammen und steuert den Telegrammverkehr. Diese werden per DMA blockweise über den Speicher der ARM ausgetauscht. Alternativ steht jedem Kanal ein Dual-Port-Memory für Statusinformationen oder als lokales Datenabbild zur Verfügung. Mit den intelligenten Kommunikations-ALUs realisiert der netX die unterschiedlichsten Protokolle und Protokoll-Kombinationen und kann diese unabhängig von den Reaktionszeiten der CPU synchronisieren - ein absolutes Novum in der industriellen Kommunikationstechnik. |

Fakten auf einen Blick

|

| Produkt | NETX 100 | |

|---|---|---|

| Beschreibung | netX 100 Netzwerk Controller | |

| Rechnerkern | ||

| Prozessor | ARM 926EJ-S, 200 MIPS, ARMv5TE-Befehlssatz mit DSP- und Java-Erweiterung | |

| Cache | 16 KByte Befehle / 8 KByte Daten | |

| Tightly Coupled Memory | 8 KByte Daten | |

| Memory Managment Unit | Windows CE- und Linux-Support | |

| Interner Speicher | ||

| RAM | 144 KByte, davon 16 KByte mit externer Spannungsversorgung | |

| ROM | 32 KByte mit Bootloader und Real-Time-Kernel | |

| Ethernet-Interface | ||

| Ports | 2 x 10BASE-T/100BASE-TX, Half-/Full-Duplex, IEEE 1588 Zeitstempel | |

| PHY | Integriert, Auto-Negotiation, Auto-Crossover | |

| Real-Time-Ethernet | EtherCAT mit drei FMMUs und vier Sync-Manager Ethernet/IP Powerlink mit integriertem Hub PROFINET RT mit integriertem Switch SERCOS-III Modbus TCP |

|

| Feldbus-Interface | ||

| Kanäle | Wird Ethernet nicht verwendet, sind zwei zusätzliche Feldbus-Interfaces verfügbar. Die Systeme können beliebig kombiniert werden. Anzahl: 1 | |

| Systeme | AS-Interface, nur Master CANopen / DeviceNet PROFIBUS, Master und Slave CC-Link, nur Slave |

|

| Peripherie | ||

| IEEE 1588 Systemzeit | 32 Bit Sekundenzähler, 32 Bit Nanosekundenzähler | |

| USB | Revision 1.1, 12 MBaud Full-Speed, Host- oder Device-Mode | |

| UART | 16550 kompatibel, max. 3 MBaud, RTS/CTS Unterstützung, Anzahl: 3 | |

| I²C | Master- und Slave Mode, 50 KHz bis 3.4 MHz, 16 Bit FIFO, Anzahl 2 | |

| SPI | Master- und Slave-Mode, max. 10 MHz, 3 Chip-Select-Signale | |

| AD-Converter | 2 x 4 Kanäle mit 1MS/s Sample&Hold und 10 Bit-Auflösung X X Single ended, Common Analog Ground, externe Referenzspannung | |

| PWM | 0–20 kHz/12 Bit-Auflösung bzw. 0–80 kHz/10 Bit-Auflösung | |

| Encoder | 2 Kanäle, Impulsvervierfachung, digitaler Eingangsfilter | |

| Allgemeine E/As | 3.3 V / 6 mA, Anzahl 16 | |

| Status LEDs | 2 LEDs zweifarbig, 3.3 V/9 mA, Anzahl 2 | |

| Speicher-Interface | ||

| Speicherbus | 32 Bit-Datenbus/24 Bit-Adressbus | |

| Adressbereich | 256 MByte SDRAM/64 MByte FLASH | |

| Speicherbausteine | SDRAM, SRAM, FLASH | |

| Host-Interface | ||

| Dual-Port-Memory Mode | 8/16 Bit-Datenbus, 64 KByte konfigurierbar in 8 Blöcke, emuliert durch internes RAM | |

| Extension-Mode | 8/16 Bit-Datenbus, 24 Bit-Adressbus, Bustiming einstellbar | |

| PIO-Mode | Frei programmierbare Ein- und Ausgänge, Anzahl: 53 | |

| Debug-Interface | ||

| JTAG | ARM-Prozessor und Boundary-Scan | |

| ETM | Embedded Trace Macrocell, ETM9 V2 Medium Size | |

| Betriebsbedingungen/Gehäuse/diverse Daten | ||

| Systemtakt | 200 MHz ARM / 100 MHz Peripherie | |

| Signalpegel | 3.3 V | |

| Spannungsversorgung | 1.5 V für Core 3.3 V für Ein-/Ausgänge |

|

| Betriebstemperatur | ohne Kühlkörper –40°C..+70°C mit Kühlkörper 10°/W –40°C..+85°C |

|

| Lagerungstemperatur | -65°C..+150°C | |

| Leistungsaufnahme | PHYs abgeschaltet typ. 1.0 W PHYs eingeschaltet, typisch 1.5 W |

|

| Gehäuse | PBGA, 1 mm Raster, 345 Pins Maße 22 x 22 mm |

|

Copyright 2014 - Hilscher

Rev: 01/19

Sie haben Ihr Passwort vergessen?

Sie haben Ihr Passwort vergessen?